なーお さんの日記

先週、D級アンプのパッシブプリの件を日記にしました。

この記事にも書きましたが、当面の目標はリレー切り替え式のリモコン化アッテネータです。

リレーの接点の品位による音質変化も気にはなりますが、音の良いと言われる接点劣化の少ないリレーは1個500円以上します。 アッテネータで使うと個数が多いので、これだけでhypexのUcD32MPアンプの本体価格と同じくらいになってしまいます。

そのため、できるだけ安いリレーということで、定番(?)のHSIN DA PRECISION の941H-2C を使います。今回はDC5V駆動なので941H-2C-5Vを使用。

しかしさすがにいきなり組み上げてしまってから出てきた音に?マークが付くと困るので、事前に2個のリレーと抵抗を組み合わせて、Lパッド型アッテネーションで音質確認をしておきました。 まあ、劣化している気もしますが、どこが劣化している、というのもわからない程度の、何となくフォーカスがぼやける感じの傾向、というだけでした。 ということで問題無しと判断、このリレーを使います。 秋月で1個100円

さて、回路のほうですが、先日仮に組んだごとうさん式の有接点ロータリーアッテネータ劣化版の回路そのままで良いか、しばし考えました。

- まずは、入力/出力インピーダンスが違うので実際に組み合わせるDACとアンプのインピーダンスで計算したい。

- リレー式なので、音質に影響のある部分への直列抵抗は極力減らせるように考えたい。

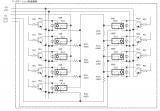

途中、不完全な回路でごとうさんのダメ出しをいただき、出来上がったのがこの回路図です。 左下のリレー1個がミソで、ここでR2側に並列に入れるようにして、R1側インピーダンスが上がりすぎるのを防いでいます。なるほどの設計ですね、さすがごとうさんです。

抵抗値の計算は、ごとうさんの案から少し変更かけて、粗々こんな感じ。これからもう少しに詰めます。

基板への実装レイアウトの検討。当初は制御回路は分けたほうが良いと思っていましたが、それよりも小型で配線長を短くする方がメリットがありそうです。 でもマイコンまで一緒に乗せるのは単に小型化したいだけなので、本当は別にすべきかなあ。

さて、肝心の使用抵抗ですが、KOAの金属皮膜抵抗(1/2W)とbispaのLGMFS(1/4W)をテストしまして、KOAは無難な音質ながら高域に少々ざらつきあり改善したい、bispaは高域は上品ですが1/4Wだったからか低域の量感が減ってしまいます。1/2Wなら大丈夫なのかな・・

bispaのLGMFSA(1/2W)に行くべきか、他のごとうさんのお勧めを試すべきか、まだ迷っています。

そして、マイコン、ARMのmbedでC/C++を3年ぶりに書くわけですが、開発環境もOSインストール時に真っ新で新たに入れなおさないといけません。(汗) プログラムが出来上がるのはいつの日か?

前の日記

前の日記